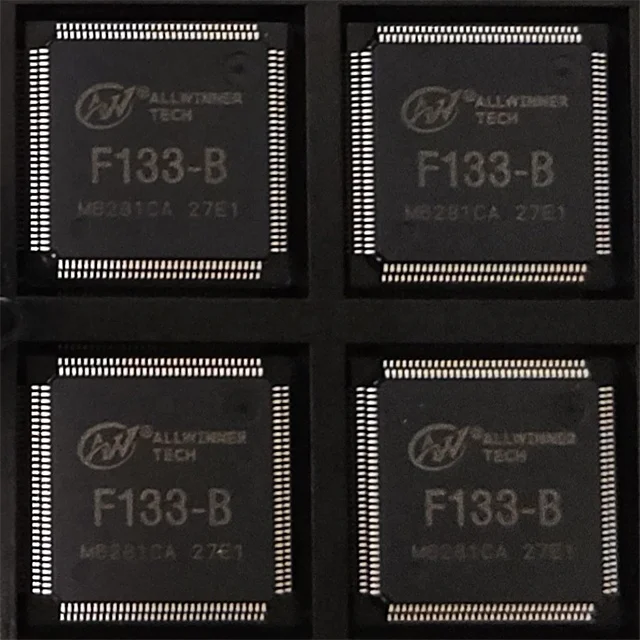

Allwinner latest video decoding processor F133 B supporting NTSC and PAL format integrates a 64 bit processor with RISC CPU

- Category: >>>

- Supplier: Shenzhen Sochip Technology Co. Ltd.

Share on (1600465650852):

Product Overview

Description

Product Description

Dear friends,

Happy to get your attention for our parts, we are Allwinner's official, core and golden distributor in China, all our selling parts are original new, with rich experienced R&D and sales team, we are willing to give you a comfortable shopping experience, please feel free to contact us at any time.

Happy to get your attention for our parts, we are Allwinner's official, core and golden distributor in China, all our selling parts are original new, with rich experienced R&D and sales team, we are willing to give you a comfortable shopping experience, please feel free to contact us at any time.

Specification

Please contact us for datasheet ^-^

F133 is allwinner's latest the Most Cost-Effective Decoding Platform Processor,

F133 is an advanced application processor designed for the video decoding platform. It

integrates a 64-bit processor with RISC CPU instruction architecture to provide the most efficient computing power. F133 supports full format decoding such as H.265, H.264, MPEG-1/2/4, JPEG, VC1, and so on. The independent hardware encoder can encode in JPEG or MJPEG. Integrated multi ADCs/DACs and I2S/PCM/DMIC/OWA audio interfaces can work seamlessly with the CPU to accelerate multimedia algorithms and provide the perfect voice interaction solution. F133 supports rich display output interfaces to meet the requirements of the screen display in differentiated markets. F133 can be used in network video machines, advertising machines,

digital photo frames, car MP5, and so on.

integrates a 64-bit processor with RISC CPU instruction architecture to provide the most efficient computing power. F133 supports full format decoding such as H.265, H.264, MPEG-1/2/4, JPEG, VC1, and so on. The independent hardware encoder can encode in JPEG or MJPEG. Integrated multi ADCs/DACs and I2S/PCM/DMIC/OWA audio interfaces can work seamlessly with the CPU to accelerate multimedia algorithms and provide the perfect voice interaction solution. F133 supports rich display output interfaces to meet the requirements of the screen display in differentiated markets. F133 can be used in network video machines, advertising machines,

digital photo frames, car MP5, and so on.

Features

RISC CPU

Memories

- Embedded with 64 MB DDR2, clock frequency up to 533 MHz

- Three SD/MMC host controller (SMHC) interfaces: SD3.0/SDIO3.0/eMMC5.0

Video Engine

-H.265/H.264/MPEG-1/MPEG-2/MPEG-4/JPEG/VC1/Xvid/Sorenso Spark decoding, up to 1080p@60fps

- JPEG/MJPEG encoding, up to 1080p@60fps Ÿ

Video and Graphics

- Allwinner SmartColor2.0 post processing for an excellent display experience

- Supports de-interlacer (DI) up to 1080p@60fps

- Supports Graphic 2D (G2D) hardware accelerator including rotate, mixer, LBC decompression functions Ÿ

Video Output

- RGB interface up to 1920 x 1080@60fps

- Dual link LVDS interface up to 1920 x 1080@60fps

- 4-lane MIPI DSI up to 1920 x 1200@60fps - CVBS OUT interface, supporting NTSC and PAL format Ÿ

Video Input

- 8-bit digital camera interface

- CVBS IN interface, supporting NTSC and PAL format (only for F133-B) Ÿ

Analog Audio Codec

- 2 DACs and 3 ADCs

- Analog audio interfaces: HPOUTL/R, MICIN3P/N, LINEINL/R, FMINL/R Ÿ

Two I2S/PCM external interfaces (I2S1, I2S2) Ÿ

Maximum 8 digital PDM microphones (DMIC) Ÿ

OWA TX and OWA RX, compliance with S/PDIF interface Ÿ

Security System

- AES, DES, 3DES, RSA, MD5, SHA, HMAC

- Integrated 2 Kbits OTP storage space Ÿ

External Peripherals

- USB 2.0 DRD (USB0) and USB 2.0 HOST (USB1)

- 10/100/1000 Mbps Ethernet port with RGMII and RMII interfaces

- Up to 6 UART controllers (UART0, UART1, UART2, UART3, UART4, UART5)

- Up to 2 SPI controllers (SPI0, SPI1)

- Up to 4 TWI controllers (TWI0, TWI1, TWI2, TWI3)

- CIR RX and CIR TX - 8 independent PWM channels (PWM0 to PWM7)

- 1-ch GPADC

- 4-ch TPADC

- LEDC Ÿ

Package

- eLQFP128, 14 mm x 14 mm x 1.4 mm

RISC CPU

Memories

- Embedded with 64 MB DDR2, clock frequency up to 533 MHz

- Three SD/MMC host controller (SMHC) interfaces: SD3.0/SDIO3.0/eMMC5.0

Video Engine

-H.265/H.264/MPEG-1/MPEG-2/MPEG-4/JPEG/VC1/Xvid/Sorenso Spark decoding, up to 1080p@60fps

- JPEG/MJPEG encoding, up to 1080p@60fps Ÿ

Video and Graphics

- Allwinner SmartColor2.0 post processing for an excellent display experience

- Supports de-interlacer (DI) up to 1080p@60fps

- Supports Graphic 2D (G2D) hardware accelerator including rotate, mixer, LBC decompression functions Ÿ

Video Output

- RGB interface up to 1920 x 1080@60fps

- Dual link LVDS interface up to 1920 x 1080@60fps

- 4-lane MIPI DSI up to 1920 x 1200@60fps - CVBS OUT interface, supporting NTSC and PAL format Ÿ

Video Input

- 8-bit digital camera interface

- CVBS IN interface, supporting NTSC and PAL format (only for F133-B) Ÿ

Analog Audio Codec

- 2 DACs and 3 ADCs

- Analog audio interfaces: HPOUTL/R, MICIN3P/N, LINEINL/R, FMINL/R Ÿ

Two I2S/PCM external interfaces (I2S1, I2S2) Ÿ

Maximum 8 digital PDM microphones (DMIC) Ÿ

OWA TX and OWA RX, compliance with S/PDIF interface Ÿ

Security System

- AES, DES, 3DES, RSA, MD5, SHA, HMAC

- Integrated 2 Kbits OTP storage space Ÿ

External Peripherals

- USB 2.0 DRD (USB0) and USB 2.0 HOST (USB1)

- 10/100/1000 Mbps Ethernet port with RGMII and RMII interfaces

- Up to 6 UART controllers (UART0, UART1, UART2, UART3, UART4, UART5)

- Up to 2 SPI controllers (SPI0, SPI1)

- Up to 4 TWI controllers (TWI0, TWI1, TWI2, TWI3)

- CIR RX and CIR TX - 8 independent PWM channels (PWM0 to PWM7)

- 1-ch GPADC

- 4-ch TPADC

- LEDC Ÿ

Package

- eLQFP128, 14 mm x 14 mm x 1.4 mm

item | value |

Model Number | F133-A |

Type | integrated circuit |

Place of Origin | China |

Guangdong | |

Brand Name | ALLWINNER |

D/C | 2021+ |

Package | eLQFP128 |

Description | F133-A processors |

Voltage - Breakdown | |

OS | Linux |

FAQ

1. who are we?

We are based in Guangdong, China, start cooperation with Allwinner from year 2006, being Allwinner's major distributor and continuously won Allwinner's prize of core partner, except for distributor, we are also a design company, we have our own development board to help customers finish their design quickly, we are also a design company, have our R&D team, you can outsource project to us, after that we can also help you make PCBA or finish goods.

2. how can we guarantee quality?

As Allwinner's official distributor, all our selling are original and new, if any Quality problem, we will ask Allwinner for replace

3.what can you buy from us?

All series of Allwinner ICs especially for V and R series, and development boards and PCBA boards.

4. why should you buy from us not from other suppliers?

Major agent of Allwinner

Rich R&D experience

powerful technical support

ODM/OEM available

5. what services can we provide?

We are based in Guangdong, China, start cooperation with Allwinner from year 2006, being Allwinner's major distributor and continuously won Allwinner's prize of core partner, except for distributor, we are also a design company, we have our own development board to help customers finish their design quickly, we are also a design company, have our R&D team, you can outsource project to us, after that we can also help you make PCBA or finish goods.

2. how can we guarantee quality?

As Allwinner's official distributor, all our selling are original and new, if any Quality problem, we will ask Allwinner for replace

3.what can you buy from us?

All series of Allwinner ICs especially for V and R series, and development boards and PCBA boards.

4. why should you buy from us not from other suppliers?

Major agent of Allwinner

Rich R&D experience

powerful technical support

ODM/OEM available

5. what services can we provide?

Fast delivery

Quality ensurance

Technical support

Tax inclusive and tax free transactions

Dedicated customer service

Dedicated customer service

We Recommend

New Arrivals

New products from manufacturers at wholesale prices