Wholesales China supplier YTS High quality custom Full Color Printing Eco friendly petg Material smart card 125Khz Card

- Category: >>>

- Supplier: Shenzhen Yintongshang Smart Card Co. Ltd.

Share on (1600624565241):

Product Overview

Description

COS developers can flexibly partition the 132 KB FLASH to store code and data.

* COS can access the high 56 KB FLASH area from XDATA. * COS can access all FLASH area from CODE, because the 64 KB limit can be surmounted by CODE banking.

To facilitate software development, the IC embeds hardware DES/ TRNG/ CRC. COS developers can enjoy smaller code size and less execution time.

For better security and reliability, the IC offers many hardware security features, e.g., high/low voltage and high/low frequency detection, etc.

Products Description

CPU | High-performance 8051-compatible 8-bit CPU | 1 instruction = 1~3 machine cycle(s) | |||||

1 machine cycle = 4 clock cycles (typical) | |||||||

CPU operating clock can be configured: | Internal clock :7.5 MHz/15 MHz/30 MHz(nominal) | ||||||

External clock: Contact smart card input CLK supply via C3 (ISO/IEC 7816) | |||||||

Memories | FLASH | Size:132KB | |||||

Page size:512 bytes | |||||||

Erase and program operation: Page Erase, Byte Program and Consecutive Bytes Program | |||||||

Typical time: Erasing 2.5ms/page, Byte programming 37μs/byte, Consecutive bytes programming 5.6ms/page | |||||||

Bit logic: 1b after erasing, 0b after programming to be 0b | |||||||

Usage: code and data * Program can surmount the 64 KB limit, using CODE Banking * High 56 KB FLASH is accessible from XDATA | |||||||

RAM | Size: 2.25KB* 2048 bytes in XDATA * 256 bytes in IDATA | ||||||

OTP | User OTP:224bytes | ||||||

SN:17 bytes | |||||||

Algorithms and Peripherals | Symmetric algorithms | DES/T-DES | |||||

Peripherals | CRC: 16-bit CRC-CCITT | ||||||

TRNG: True Random Number Generator, for secure transactions | |||||||

Timer: One 16-bit timer, one ETU timer | |||||||

Interfaces | ISO/IEC 7816-3 serial interface | UART supporting ISO/IEC 7816-3 T=0/T=1 protocol and 11 baud rates: F/D = 11H, 12H, 13H, 18H, 91H, 92H, 93H, 94H, 95H, 96H, 97H | |||||

Support GSM power consumption standards, including Clock Stop mode | |||||||

Security | Scrambling data storage | ||||||

High/low voltage and high/low clock frequency detectors | |||||||

CLK filter(ISO/IEC 7816 external clock) | |||||||

Power glitch detectors | |||||||

Security Certification: EAL4+ | |||||||

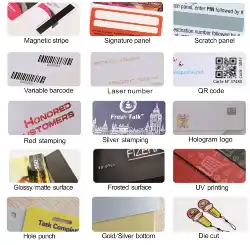

Details Images

Product Paramenters

13.56 Mhz RFID printable smart card NFC contactless cards pvc blank card

1. Different chips are available for your card.

2. Accept customzied printing and logo.

3. PVC plastic material Rfid NFC card is waterproof and cost effective.

4. Meet different requirements for different applications, such as access control for hotel & office, identity, etc.

5. Our RFID NFC cards have been widely exported to different countries, including North America, Europe, Middle East, Africa, etc. Highly approved by different clients.

1. Different chips are available for your card.

2. Accept customzied printing and logo.

3. PVC plastic material Rfid NFC card is waterproof and cost effective.

4. Meet different requirements for different applications, such as access control for hotel & office, identity, etc.

5. Our RFID NFC cards have been widely exported to different countries, including North America, Europe, Middle East, Africa, etc. Highly approved by different clients.

Product packaging

Company Profile

YTS SMART CARD monthly produces over 30 million cards and distributes them to more than 50 countries worldwide. RFID card normal for Hotel locking uses RFID system or magnetic stripe system. For RFID locking system,

high frequency (13.56MHz) under protocol ISO 14443A is the most popular choice for the majority of hotels.

high frequency (13.56MHz) under protocol ISO 14443A is the most popular choice for the majority of hotels.

Each RFID chip has a unique ID code, in which high frequency and ultra high frequency chips can also be written according to customer needs.Based on the characteristics of RFID, the mainstream applications on the market are very extensive.

Hotel partner: Vienna hotel, LaCrosse hotel, Hanting inns & hotels, Mercure Hotel, Travelodge hotel & Four Seasons Resort hotel etc.

Hotel partner: Vienna hotel, LaCrosse hotel, Hanting inns & hotels, Mercure Hotel, Travelodge hotel & Four Seasons Resort hotel etc.

Printing equipment: Heidelberg offset printing machine with UV passageway HP Indigo Digital printing machine -for a personalized design, especially for the Photo ID Card.

Printing effect: YTS SMART CARD understands Printing the s key issue to meet client’s satisfaction.

Therefore we print cards strictly according to client’s layout. Keeping the consistency between printing effect and approved layout is always the priority for us.

Therefore we print cards strictly according to client’s layout. Keeping the consistency between printing effect and approved layout is always the priority for us.

Available Crafts: Hot stamp (gold/silver/red), Laser silver/gold, Laser Engraving, Inkjet printing, Scratch off-panel, Barcode/QR code, Thermal printing, Hologram, Embossing, Adhesive sheet, UV ink, Hologram, Hole punch, etc.

Application Area: widely used for promoting, social meida, identification, access control, marketing, loyalty, hospitality & Hotel locking etc.

Certifications

FAQ

Q1. CAN YOU OFFER US FEW SAMPLES ?

A:After we know clearly what products you need, then we can offer similar existing sample for your reference.

Sample free with shipping cost you paid.

If you need customized tag sample based on your design and requirement,there is reasonable samplecost charged accordingly.

Sample free with shipping cost you paid.

If you need customized tag sample based on your design and requirement,there is reasonable samplecost charged accordingly.

Q2. WE ARE NOT AN EXPERT BUYER IN YOUR TECHNOLOGY, WHAT INFORMATION DOYOU NEED FROM US TO QUOTE ?

A:Dear friend, please inform us clearly the tag's application, what goal do you want to achieve,

we would propose you the suitable product in good price

we would propose you the suitable product in good price

Q3. WE HAVE A CONCERN THAT WE PAID, BUT YOU DON'T SEND US THE GOODS .

A:We are a leading company doing honest business in the internat market for years.We always get positive feedback from our worldwide customers.Furthermore, our company support Trade Assurance on Alibaba,

you can place order through Alibaba that guarantees your money safe and order go smoothly.

you can place order through Alibaba that guarantees your money safe and order go smoothly.

Q4. Are you a manufacturer or trading company? CAN WE VISIT YOUR FACTORY ?

A:Yes, we are professional rfid smart card manufacture since 2005.Warmly welcome your factory tour. And it's honored to be your guide in your China trip.

Q5.Can I print our logo/ barcode/ unique QR code/ series number on your cards?Or can you customize my RFID card in special shape?

A: Yes, of course. We do customized products.

Q6.How can you make sure we will receive the RFID card with high quality?

A:Our QC team will inspect each batch of RFID card before delivery and all the raw material we used are eco-friendly,

we have certificates of ISO9001-2008,SGS,ROHS,EN71 etc

we have certificates of ISO9001-2008,SGS,ROHS,EN71 etc

We Recommend

New Arrivals

New products from manufacturers at wholesale prices